硬件路由器实验板上有几片型号为IS61WV102416BLL-10TLI的SRAM, 若不添加时序约束, 很有可能导致布线不满足时序要求, 同时无法给出相应的时序分析报告, 从而造成“玄学”问题。为此, 前几天我在写上电自检代码中操作SRAM的部分的时候, 尝试添加了时序约束, 不知道有没有写对, 特此记录一下。敬请各位读者批评指正!

具体而言, 简单来看, 这个SRAM的读取延迟为10ns, 即地址(包括其他控制信号, 下同)在SRAM的地址引脚准备好后, 过10ns之后, 读取的正确的数据会出现在SRAM的数据引脚。此处, 我将其看成一个组合逻辑, 下文尝试使用set_input_delay和set_output_delay设置时序约束。假设在FPGA的逻辑中, 地址由一组D触发器输出, 数据输入后立即进入到另一组D触发器。

首先回顾一下set_input_delay和set_output_delay的作用。假设tperiod为时钟周期, tsetup为D触发器的建立时间, 时钟信号传播延迟忽略不计。

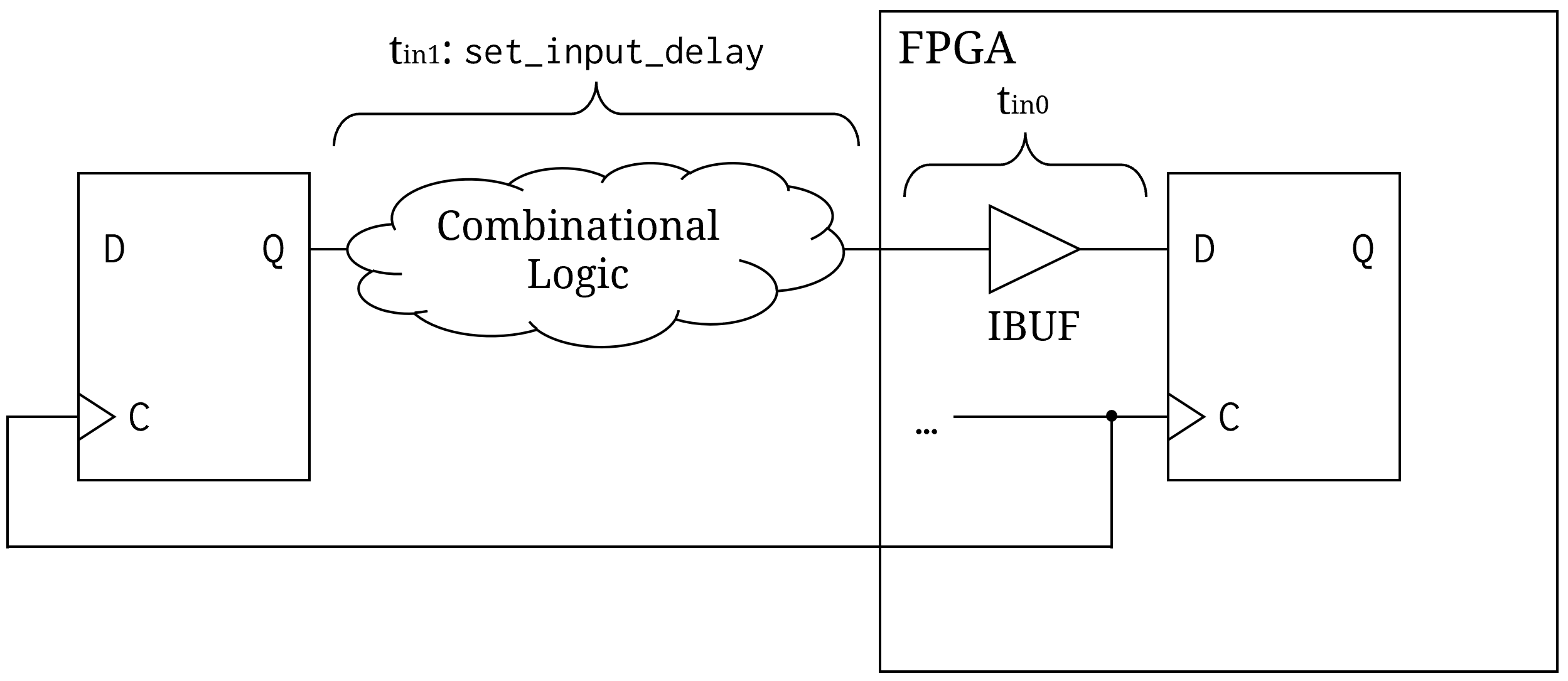

如下图所示, 对于set_input_delay, 为了使得片外元件的D触发器输入到FPGA的D触发器的信号能够被正确采样, 即FPGA的触发器的建立时间得以满足, 需要将片外的延迟信息提供给分析器(综合器)。

其中, tin0为FPGA内部的输入延迟, 分析器附带的FPGA模型能够提供; tin1为通过set_input_delay设置的额外的输入延迟。此时, 应当要求: tin0 + tin1 < tperiod – tsetup 在此约束下, 编译器会调整布局布线, 从而改变tin0来满足约束。

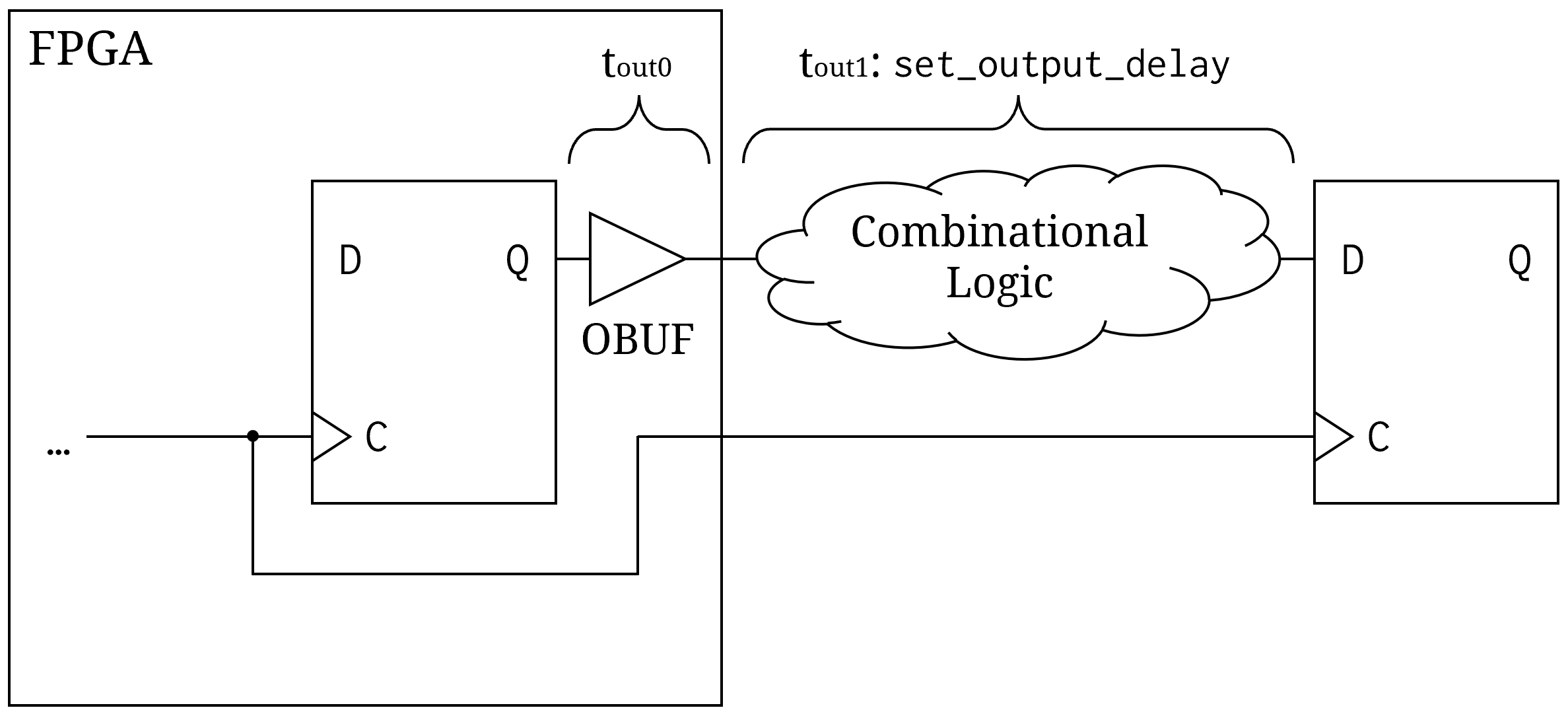

类似地, 如下图所示, 对于set_output_delay, 为了使得FPGA输出到一个片外元件的D触发器的信号能够被正确采样, 即片外元件的触发器的建立时间得以满足, 需要将片外的延迟信息提供给分析器。

其中, tout0为FPGA内部的输出延迟, 分析器附带的FPGA模型同样能够提供; tout1为通过set_output_delay设置的额外的输出延迟。此时, 应当要求: tout0 + tout1 < tperiod – tsetup 在此约束下, 编译器会调整布局布线, 从而改变tout0来满足约束。

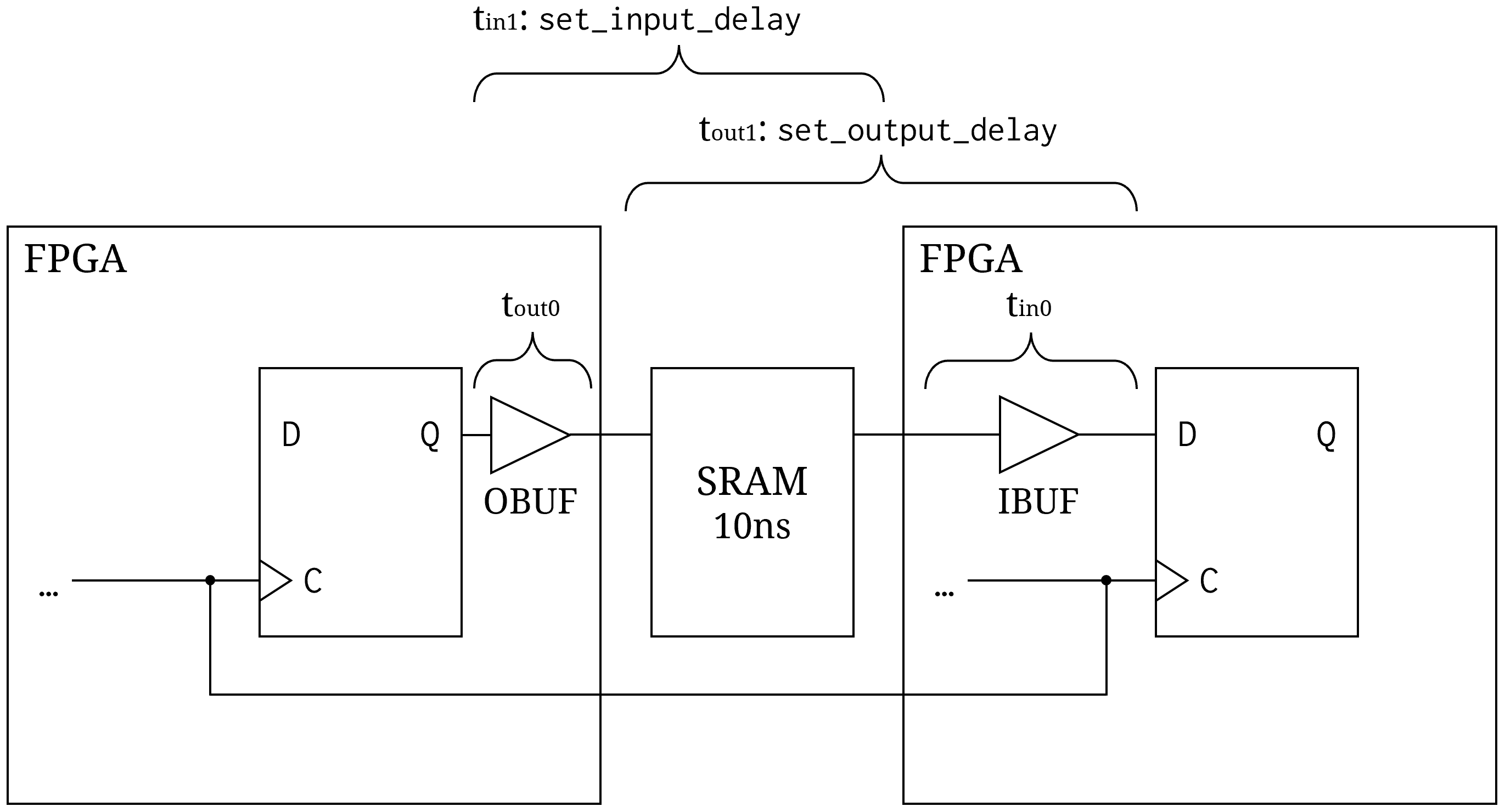

现在, 考虑一开始提到的SRAM, 信号的传播路径是FPGA的D触发器输出—SRAM—FPGA的另一组D触发器输入, 如下图所示。其中, 两个FPGA为同一个, 为了方便, 我将它拆开绘制了。

然后, 根据上文所述的理论, 应当设置时序约束, 令tin1 = tout0 + 10ns, tout1 = tin0 + 10ns。然而, tin0以及tout0的取值在编写时序约束时事实上是不清楚的。此处, 我先强行令tin1 = tout1 = tperiod – tsetup, 通过阅读此时的时序分析报告(一定是失败的)可以得知tin0以及tout0的大致取值, 然后重新设置时序约束即可。虽然根据约束不同, 这两个值会有变化。顺便指出, 经过实践, tin0以及tout0的大致取值分别为<4ns及<9ns。后来, 我按照5ns和10ns编写的时序约束。

最后, 作为一个具体的例子, 假设采用了40MHz的时钟, 其周期为25ns, 可以采用如下代码来设置约束:

# Input/Output Delay for SRAM.

# Make sure that input delay + output delay - 10 == clock period

set_input_delay -clock ram_clk -max 20.000 [get_ports {ram_data[*]}]

set_output_delay -clock ram_clk -max 15.000 [get_ports {ram_data[*]}]

set_output_delay -clock ram_clk -max 15.000 [get_ports {ram_addr[*]}]

set_output_delay -clock ram_clk -max 15.000 [get_ports {ram_be_n[*]}]

set_output_delay -clock ram_clk -max 15.000 [get_ports ram_ce_n]

set_output_delay -clock ram_clk -max 15.000 [get_ports ram_oe_n]

set_output_delay -clock ram_clk -max 15.000 [get_ports ram_we_n]

此外, 对于SRAM的写操作, 地址和数据可以一并输出, 并且后续FPGA不需要再从SRAM输入数据, 因此时序约束相对简单。事实上, 其中的挑战在于SRAM要求写使能信号(/WE)被地址和数据完全覆盖, 即写使能信号应当在地址和数据稳定后给出(拉低), 而在地址或数据变化前撤除(拉高)。这一点又需要用到其他神奇的方法, 本文就不过多讨论了。

发表评论